注意:ADS 2015.01 提供了对 ADS 版图中的原生 ODB ++导入和 EM 设置的增强,使得 W2324大容量版图预处理器逐渐淘汰,因为它的功能已被最新版本的 ADS 版图取代。

- 获取报价截止日期:2015 年 3 月 31 日

- 订购永久性和限时许可证(TBL)的截止日期:2015 年 7 月 31 日

- 订购支持截止日期:2016 年 7 月 31 日

先进设计系统(ADS)大容量版图预处理器组件为高速数字设计流程提供了以下功能:

- 将 ODB++ 格式的 PCB 设计文件导入到预处理器的图形用户界面中

- 支持选择关键网络和进行 cookie 剪切

- 使用 Momentum 和 FEM 组件把经过处理的 PCB 部分导出到 ADS 版图,进行电磁建模

- 支持导入网络名和元器件

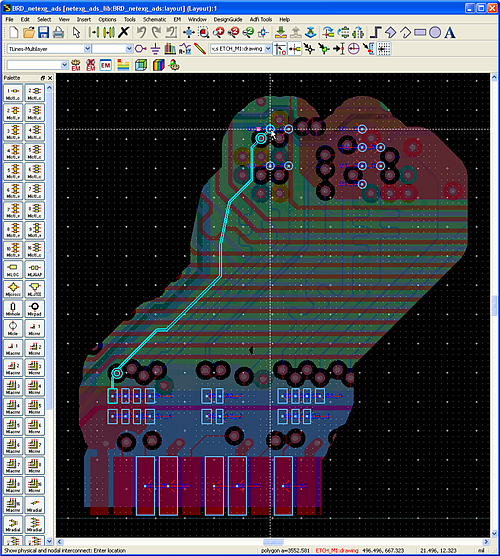

大容量版图预处理器组件是一款支持 ODB++ 文件格式的导入和预处理工具,可让您选择关键网络的周边环境,为电磁(EM)建模做好准备。在高速数字设计中,如果印刷电路板(PCB)的结构非常复杂,并且整体几何结构过于庞大,超出电磁场求解程序的计算能力时,执行此类预处理将带来极大帮助。此解决方案主要针对少数关键网络而设计;例如,一个差分对把两个串行器/解串器(SERDES)集成电路(IC)连接在一起,它会受到一个或多个干扰源走线的串扰影响。图 1 显示了一个走线示例。请注意:电路板已经过“cookie 剪切”,这意味着凸包已经定义完毕,其裕量由用户自定义,剩下一部分电路板可以由全精度、全波电磁场求解程序(例如 Momentum 和 FEM 组件)来处理。

图 1. 青色突出显示了一个关键网络,这样的关键网络还有几个。请注意:这个大型 PCB 已经过了“cookie 剪切”。左侧边沿处是一个凸包,包括最左侧的网格和附近的裕量。

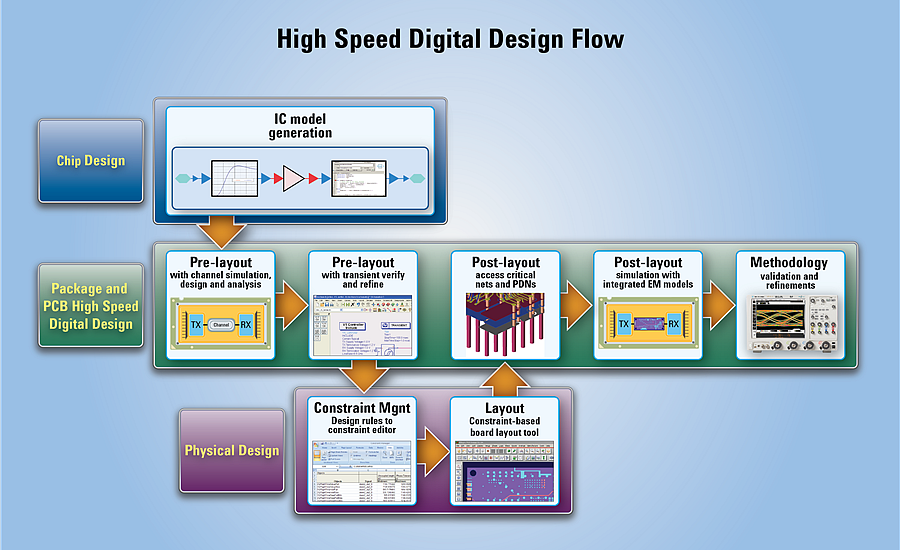

图 2 显示了典型的高速数字工作流程,包括大容量版图预处理器组件。

图 2. 大容量版图预处理器是这个高速数字设计流程的核心。中间方框(绿色)显示了信号完整性工程师在 ADS 中的操作步骤,而下方方框(紫色)显示了物理设计工程师在第三方企业级 PCB 工具中的操作步骤。上方方框(蓝色)显示了芯片设计人员所执行的操作步骤。

首先,信号完整性工程师把厂商提供的 IC 模型与通道的前期版图“占位符”结合在一起。一般来说,占位符是在 ADS 多层模型(MLM)传输线程序库中生成,可能与过孔电磁模型互为补充。前期版图仿真的目的是探索设计空间,优化 IC 设置(例如发射机(Tx)SERDES 预加重滤波器抽头和接收机(Rx)SERDES 等化器抽头以及时钟/数据恢复(CDR)电路设置)、堆叠、可控阻抗线几何结构以及过孔设计。

物理设计工程师可将这些参数加载到第三方企业级 PCB 工具(例如明导国际的 Expedition)的自动路由器的约束编辑器中。在对电路板进行路由时,这些工具可提供 ODB++ 文件格式的后期版图原图。

信号完整性工程师选择关键网络,并对 PCB 的重点部分进行预处理,以便进行电磁建模。再用得到的电磁模型“置换出”前期版图的占位符,它具有后期版图设计的真实特征。通过这种方法,您可以在投产之前对候选版图进行验证。如果候选设计存在过度串扰等问题,信号完整性工程师能够调整 ADS 版图“沙盒”的临界面积(例如,通过添加缝合孔或防护走线),并对新的候选设计进行求解,直至达到令人满意的调整效果。物理设计工程师可将从 ADS 实验中得到的“知识”应用到第三方企业级 PCB 工具的“理想”设计副本中,以确保设计一次性通过测试。在检验后期版图时(即按顺序制造多个原型并进行测量),这种方法可以避免昂贵、耗时而且不确定的“试误”法。